# 2.5" Tiger IDE Solid State Drive

# **Product Specification**

Version 1.3

December 2009

PRETEC/C-ONE Technology Corp.

Corporate Headquarters 8F, NO5, Lane 345, Yang Guang St., Neihu, Taipei,Taiwan TEL: +886-2-2659-4380 Fax: +886-2-2659-4390

www.pretec.com

# **Document Version**

| Version | Description      | Date         | Editor      | Approved by |

|---------|------------------|--------------|-------------|-------------|

| 1.0     | New issued       | 20,Dec.,2008 | Matika Wang | David Lin   |

| 1.2     | Add new capacity | 18,Sep.,2009 | Matika Wang | David Lin   |

| 1.3     | Modify           | 8,Dec.,2009  | Amos Chung  | Kent Liu    |

This document provides information regarding to Pretec 2.5" Tiger IDE Solid State Drive product specification and is subject to change without any prior notice. No part in this report shall be distributed, reproduced, or disclosed in whole or in part without prior written permission of Pretec.

All rights reserved. Pretec/C-ONE Technology Corp.

# Contents

| 1. INTRODUCTION                                           | 4  |

|-----------------------------------------------------------|----|

| 1.1 GENERAL DESCRIPTION                                   | 4  |

| 1.2 Features                                              | 4  |

| 1.3 Part Number Definition                                | 5  |

| 2. PRODUCT SPECIFICATION                                  | 6  |

| 2.1 OPERATION AND ENVIRONMENT DESCRIPTION                 | 6  |

| 2.2 PHYSICAL DESCRIPTION                                  | 6  |

| 3. SUPPORT FLASH MEDIA                                    | 7  |

| 3.1 Supported NAND Flash Type                             | 7  |

| 3.2 Logical Format Parameters (CHS)                       | 7  |

| 4. BLOCK DIAGRAM                                          | 8  |

| 4.1 Controller Archive                                    | 8  |

| 4.2 Flash Card Archive                                    | 8  |

| 5. SPECIFICATION AND FEATURES                             | 9  |

| 5.1 Physical Specification                                | 9  |

| 6. PIN ASSIGNMENT                                         | 10 |

| 6.1 PIN TYPE                                              |    |

| 6.2 INTERFACE SIGNALS DESCRIPTION                         |    |

| 6.3 INSTALLING THE SSD DRIVE IN A TWO-DRIVE CONFIGURATION |    |

| 7. ATA SPECIFIC REGISTER DEFINITIONS                      | 14 |

| 7.1 True IDE Mode                                         | 14 |

| 7.2 ATA REGISTERS                                         | 14 |

| 7.2.1 Data Register                                       | 14 |

| 7.2.2 Error Register                                      | 14 |

| 7.2.3 Feature Register                                    | 15 |

| 7.2.4 Sector Count Register                               | 15 |

| 7.2.5 Sector Number Register                              | 16 |

| 7.2.6 Cylinder Low Register                               | 16 |

| 7.2.7 Cylinder High Register                              | 16 |

| 7.2.8 Drive Head Register                                 |    |

| 7.2.9 Status Register                                     |    |

| 7.2.10 Alternate Status Register                          |    |

| 7.2.11 Device Control Register                            |    |

| 7.2.12 Drive Address Register                             | 18 |

# 1. Introduction

### **1.1 General Description**

Pretec 2.5" Tiger IDE Solid State Drive (SSD) uses NAND-Type flash memory devices, which leads to its remarkable high performance and comes with capacities from 512MB to 32GB unformatted.

Compliant with ISA (Industrial Standard Architecture) bus interface standard, the IDE SSD performs sequential read/write for each sector (512 bytes) count. It also conforms to IDE Specification and is designed with precision mechanics to enable host devices to read/write from the IDE interface into Flash Media. It can operate with a 5V single power from the host side.

The card provides extraordinary memory medium for PC, Pretec 2.5" Tiger IDE SSD has been approved through various compatibility tests.

### 1.2 Features

■ IDE interface

ATA command set compatible

Support for 8-bit or 16-bit host data transfer

Compatibility with host ATA disk I/O BIOS, DOS/Windows file system, utilities and application software

- Extremely rugged and reliable Advanced defect block management Support background erased operation

- 5 Volt power supply, very low power consumption Zero-power data retention, no batteries required Internal self-diagnostic program operates at VCC power on Auto sleep mode

- High reliability based on internal ECC (Error Correcting Code) function

- Mode access

- PIO Mode 4

- UDMA Mode 4

### **1.3 Part Number Definition**

### $X_1 X_2 \, X_3 \, X_4 X_5 \, X_6 \, X_7 \, X_8$

| Code   | Definition        | symbol | Description                     |

|--------|-------------------|--------|---------------------------------|

| X1X2   | Interface         | IE     | 2.5" IDE                        |

| X3     | Solution          | М      | Tiger Series                    |

|        |                   | 512    | 512MB                           |

|        |                   | 01G    | 1GB                             |

|        |                   | 02G    | 2GB                             |

| X4X5X6 | Capacity          | 04G    | 4GB                             |

|        |                   | 08G    | 8GB                             |

|        |                   | 16G    | 16GB                            |

|        |                   | 32G    | 32GB                            |

|        |                   | С      | Commercial Grade 0°C ~ 70°C     |

| X7     | Temperature Range | L      | Light Grade -20°C ~ 85°C        |

|        |                   | Н      | Heavy Grade -40°C ~ 85°C        |

| X8     | Appearance        | 0      | 40-pin to 44-pin IDE Flat Table |

| ~0     | Appearance        | 4      | 44-pin to 44-pin IDE Flat Table |

Notes:

1. IEMxxxC4-S for Super thin Model - thickness 5.8mm

# 2. Product Specification

# 2.1 Operation and Environment Description

| Operating Voltage                 | DC Input Power                | 5V ±                           | 10%                 |

|-----------------------------------|-------------------------------|--------------------------------|---------------------|

|                                   |                               | Read Mode: 60 mA               | (Max.)              |

| <b>Typical Power Consumptions</b> | 5V                            | Write Mode: 75 mA(             | Max.)               |

|                                   |                               | Standby Mode: 18 n             | nA(Approach values) |

|                                   | Operating Temperature         | Extended Temp.                 | -20°C to +85°C      |

|                                   | Operating temperature         | Industrial Temp.               | -40°C to +85°C      |

|                                   | Ctore ao Tomporaturo          | Extended Temp.                 | -40°C to +90°C      |

|                                   | Storage Temperature           | Industrial Temp.               | -50°C to +90°C      |

| Environment conditions            | Humidity Operation            | 5% to 95% (Non-condensing)     |                     |

| Environment conditions            | Humidity Non-operation        | 5% to 95% (Non-condensing)     |                     |

|                                   | Shock Operation               | 3000-G (Max.)                  |                     |

|                                   | Shock Non-operation           | 3000-G (Max.)                  |                     |

|                                   | Vibration Operation           | 30-G (Peak to peak to maximum) |                     |

|                                   | Vibration Non-operation       | 30-G (Peak to peak to maximum) |                     |

| Operation System supported        | DOS, Windows 98/2000/XP/Vista |                                |                     |

Notes:

1. For extended and industrial support, please contact account sales for industrial solution

## 2.2 Physical Description

| Measurement        | 2.5" Tiger IDE SSD  | 69.85mm(L) x 100.2mm(W) x 5.8mm(H) or              |

|--------------------|---------------------|----------------------------------------------------|

| weasurement        | 2.5 TIGETIDE 33D    | 69.85mm(L) x 100.2mm(W) x 12.5mm(H)                |

| Storage Capacities | Capacitance         | 512MB to 32GB (unformatted)                        |

| Performance        | Data Transfer Rates | 35MB/S(Read)                                       |

| Ferrormance        |                     | 25MB/S(Write)                                      |

|                    | MTBF                | 3,000,000 hours                                    |

| Reliability        | Error Correction    | Error Correcting of 4 bits random error per sector |

| Reliability        | D/M/ Teat           | Test disk:                                         |

|                    | R/W Test            | 3,000,000 Read/Write cycles                        |

# 3. Support Flash Media

### 3.1 Supported NAND Flash Type

### 3-1-1 Small block size of 16KB

| Flash Capacity 128Mb |  | 256Mb        | 512Mb |

|----------------------|--|--------------|-------|

| Operation Voltage    |  | 2.7V to 3.6V | ,     |

**Unit: Bits**

#### 3-1-2 Large block size of 128KB

| Flash Capacity    | 1Gb | 2Gb  | 4Gb       | 8Gb |

|-------------------|-----|------|-----------|-----|

| Operation Voltage |     | 2.7\ | ′ to 3.6V |     |

**Unit: Bits**

### 3.2 Logical Format Parameters (CHS)

| Card Density <sup>*1</sup>          | 512MB                    | 1GB           | 2GB           | 4GB           |

|-------------------------------------|--------------------------|---------------|---------------|---------------|

| Cylinder                            | 999                      | 1,999         | 3,998         | 7,931         |

| Heads                               | 16                       | 16            | 16            | 16            |

| Sectors/Track <sup>*2</sup>         | 63                       | 63            | 63            | 63            |

| Total<br>Sectors/Card <sup>*3</sup> | 1,006, <mark>9</mark> 92 | 2,014,992     | 4,029,984     | 7,994,448     |

| Capacity <sup>*4</sup>              | 514,850,816              | 1,030,750,208 | 2,062,548,992 | 4,092,592,128 |

Unit: Bytes

| Card Density       | 8GB           | 16GB           | 32GB           |

|--------------------|---------------|----------------|----------------|

| Cylinder           | 15,863        | 16,383         | 16,383         |

| Heads              | 16            | 16             | 16             |

| Sectors/Track      | 63            | 63             | 63             |

| Total Sectors/Card | 15,989,904    | 16,514,064     | 16,514,064     |

| Capacity           | 8,186,232,832 | 16,373,514,240 | 32,748,077,056 |

**Unit: Bytes**

Notes:

<sup>\*</sup>1. It's the logical address capacity including the area which is used for file system.

- <sup>\*</sup>2. Total tracks = number of head x number of cylinder.

- <sup>\*</sup>3. Total sector/Card = sector/track x number of head x number of cylinder.

- <sup>\*</sup>4. Those are general unformatted capacity of all cards.

# 4. Block Diagram

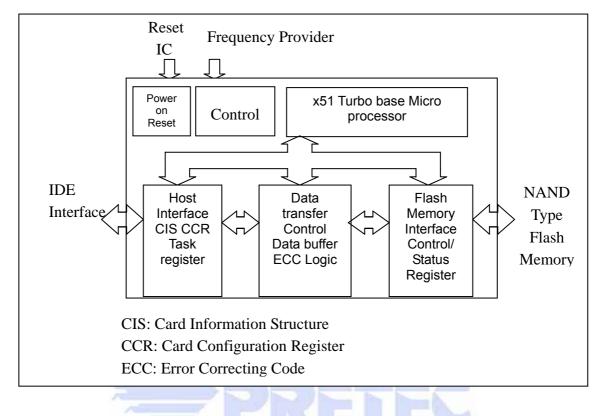

### 4.1 Controller Archive

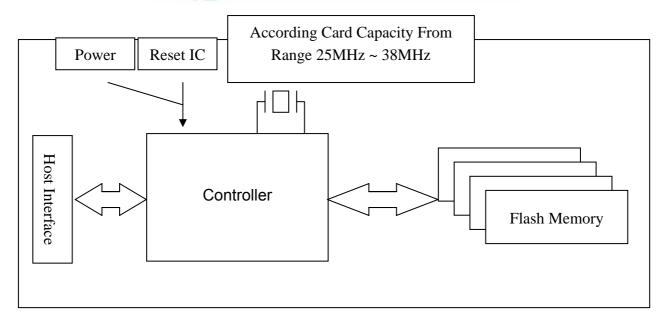

### 4.2 Flash Card Archive

# 5. Specification and Features

## 5.1 Physical Specification

Figure 1: Mechanical Dimensions of 2.5" Tiger IDE SSD (H = 12.5mm)

Figure 2: Mechanical Dimensions of 2.5" Tiger IDE SSD (H = 5.8mm)

# 6. Pin Assignment

# 6.1 Pin Type

| Pin Num. | Signal Name | Pin Type          | Pin Num. | Signal Name | Pin Type          |

|----------|-------------|-------------------|----------|-------------|-------------------|

| А        | GND         | Ground            | В        | NSCEL       | I                 |

| С        | #Slave      | I                 | D        | NSCEL       | I                 |

| E        | Кеу         | Cut Pin           | F        | Кеу         | Cut Pin           |

| 1        | #Reset      | I                 | 2        | GND         | Ground            |

| 3        | Data 7      | I/O               | 4        | Data 8      | I/O               |

| 5        | Data 6      | I/O               | 6        | Data 9      | I/O               |

| 7        | Data 5      | I/O               | 8        | Data 10     | I/O               |

| 9        | Data 4      | I/O               | 10       | Data 11     | I/O               |

| 11       | Data 3      | I/O               | 12       | Data 12     | I/O               |

| 13       | Data 2      | I/O               | 14       | Data 13     | I/O               |

| 15       | Data 1      | I/O               | 16       | Data 14     | I/O               |

| 17       | Data 0      | I/O               | 18       | Data 15     | I/O               |

| 19       | GND         | Ground            | 20       | Кеу         | Cut Pin           |

| 21       | DMARQ       | 0                 | 22       | GND         | Ground            |

| 23       | #IOW        | I                 | 24       | GND         | Ground            |

| 25       | #IOR        | I                 | 26       | GND         | Ground            |

| 27       | IORDY       | I                 | 28       | CSEL        | I                 |

| 29       | DMACK       | I                 | 30       | GND         | Ground            |

| 31       | IRQ         | 0                 | 32       | #IOCS16     | 0                 |

| 33       | A1          | I                 | 34       | #PDIAG      | I/O               |

| 35       | A0          | I                 | 36       | A2          | I                 |

| 37       | #CS0        | I                 | 38       | #CS1        | I                 |

| 39       | #DASP       | I/O               | 40       | GND         |                   |

| 41       | Vcc         | Supply<br>Voltage | 42       | Vcc         | Supply<br>Voltage |

| 43       | GND         | Ground            | 44       | TYPE        |                   |

# 6.2 Interface Signals Description

| Signal<br>Name | Pin    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #SLAVE         | A,C    | I   | SLAVE<br>Pins A and C are pulled-up input pins that are shorted together internally.<br>(Pins B and D are ground.) These pins are used to configure the SSDdrive<br>as Slave device. When all pins A, B, C and D are grounded, the SSDdrive<br>is also configured as a Slave device. If both pins A and B remain open, the<br>SSDdrive is configured as a Master or as the only drive in a single drive<br>system. |

| #RESET         | 1      | I   | HOST RESET<br>Reset signal from the host that is active on power up and inactive<br>thereafter.                                                                                                                                                                                                                                                                                                                    |

| Data<br>(15-0) | 3 - 18 | I/O | HOST DATA15-0<br>These 16 lines carry the Data between the controller and the host. The low<br>8 lines transfer commands, status, and ECC information between the host<br>and the controller.                                                                                                                                                                                                                      |

| DMARQ          | 21     | 0   | DMA REQUEST<br>When ready to transfer data to or from the host, this signal used for DMA<br>data transfers between host and device, shall be asserted by the device.                                                                                                                                                                                                                                               |

| #IOW           | 23     | I   | I/O WRITE<br>This strobe pulse is used to clock data or commands on the host data bus<br>into the controller. The clocking will occur on the negative to positive edge<br>of the signal (trailing edge).                                                                                                                                                                                                           |

| #IOR           | 25     | I   | I/O READ<br>This is a read strobe generated by the host. This signal gates data or<br>status on the host bus and strobes the data from the controller into the<br>host on the low to high transition (trailing edge).                                                                                                                                                                                              |

| IORDY          | 27     | I   | I/O READY<br>This signal is negated to extend the host transfer cycle of any host register<br>access (Read or Write) when the device is not ready to respond to a data<br>transfer request.                                                                                                                                                                                                                        |

| Vcc            | 41,42  |     | +5 V POWER                                                                                                                                                                                                                                                                                                                                                                                                         |

| Signal<br>Name | Pin                            | I/O | Description                                                                                                                                                                                            |

|----------------|--------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSEL           | 28                             | I   | CABLE SELECT<br>When grounded, the device is configured as a Master. When opened, this<br>device is configured as a Slave.                                                                             |

| DMACK          | 29                             | I   | DMA ACKNOWLEDGE<br>This signal shall respond to DMARQ by the host to initiate DMA transfers.                                                                                                           |

| IRQ            | 31                             | 0   | INTERRUPT REQUEST<br>This is an interrupt request from the controller to the host, asking for<br>service. The output of this signal is tri-stated when the interrupt are<br>disabled by the host.      |

| #IOCS16        | 32                             | 0   | I/O SELECT 16<br>This open drain output is asserted low to indicate to the host the current cycle is a 16-bit word data transfer.                                                                      |

| #PDIAG         | 34                             | I/O | PASS DIAGNOSTIC<br>After an Execute Diagnostic command to indicate to the master it has<br>passed its diagnostics, this bi-directional open drain signal is asserted by<br>the slave.                  |

| A (2-0)        | 33,35,36                       | -   | HOST ADDRESS 2-0<br>These address lines are used to select the registers within the controller<br>task file.                                                                                           |

| #CS0           | 37                             | I   | HOST CHIP SELECT 0<br>A chip select signal used to select the controller task file.                                                                                                                    |

| #CS1           | 38                             | I   | HOST CHIP SELECT 1<br>A chip select signal that is used to select the control and diagnostic<br>register.                                                                                              |

| #DASP          | 39                             | I/O | DISK ACTIVE/SLAVE PRESENT<br>This open drain output signal is asserted low any time the drive is active.<br>In a master/slave configuration, the slave uses it to inform the master of its<br>present. |

| NC             | E,F,20                         | -   | These pins are reserved for the connector keys.                                                                                                                                                        |

| GND            | A,D,2,19,22,<br>24,26,30,40,43 |     | GROUND                                                                                                                                                                                                 |

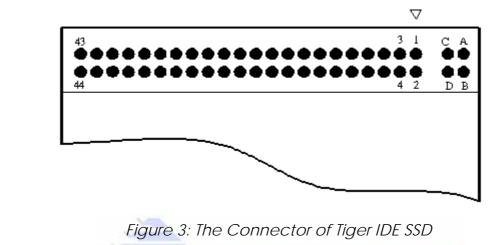

### 6.3 The Jumper Setting of Tiger IDE SSD

The Tiger IDE SSD can be configured as Primary (Master), Secondary (Slave) and Cable Select mode.

Cable Select mode: If pin A and B are jumped, the drive is installed as the Cable Select drive.

**Primary (Master) mode**: If pin C and D are jumped, the drive is installed as the Primary (Master) drive.

Secondary (Slave) mode: Either pin AC or none of the pins should be grounded, the drive is installed as the Secondary (Slave) drive.

**Cable Select:** Secondary (Slave): 43..5 3 CA 43.53 1 CA 1 00 0 00 Ο 00 Ο  $\bigcirc lacksquare$ Ο  $\bigcirc$ 000 00 Ο 00 Ο  $\bigcirc \bullet$ 44..642 DB 44...64 2 D B If pin A and B are jumped, the drive is configured as Cable Select drive 43..5 3 1 CA 0 0 0Ο Primary (Master): Ο 0 0 0 00 43..5 3 1 CA 44..642DB Ο Ο Ο Ο  $\bullet \circ$ If all pins A, B, C, and D are open, or pin A Ο 000  $\bullet \circ$ and C are jumped, the drive is configured as 44...642 DB Secondary (Slave) drive

If pin C and D are jumped, the drive is configured as Primary (Master) drive

# 7. ATA Specific Register Definitions

As we described the adapter provides several kinds of addressing modes, Memory mode, I/O mode, and True IDE mode. Below are described the procedures access for accessing each mode the Task File registers.

### 7.1 True IDE Mode

| #CS0 | #CS1 | DA2 | DA1 | DA0          | #IORD = "0"      | #IOWR = "0"    |

|------|------|-----|-----|--------------|------------------|----------------|

| 1    | 1    | Х   | Х   | Х            | Hi-Z             | Not Used       |

| 1    | 0    | 0   | Х   | Х            | Hi-Z             | Not Used       |

| 1    | 0    | 1   | 0   | Х            | Hi-Z             | Not Used       |

| 0    | 0    | Х   | Х   | Х            | Invalid          | Invalid        |

| 1    | 0    | 1   | 1   | 0            | Alternate Status | Device Control |

| 1    | 0    | 1   | 1   | 1            | Device Address   | Not Used       |

| 0    | 1    | 0   | 0   | 0            | Data             | Data           |

| 0    | 1    | 0   | 0   | 1            | Error            | Feature        |

| 0    | 1    | 0   | 1   | 0            | Sector Count     | Sector Count   |

| 0    | 1    | 0   | 1   | 1            | Sector Number    | Sector Number  |

| 0    | 1 🕥  | 1   | 0   | 0            | Cylinder Low     | Cylinder Low   |

| 0    | 1    | 1   | 0   | 1            | Cylinder High    | Cylinder High  |

| 0    | 1 🔿  | 1   | 1   | 0 Drive/Head |                  | Drive/Head     |

| 0    | 1    | 1   | 1   | 1            | Status           | Command        |

### 7.2 ATA Registers

### 7.2.1 Data Register

The Data register is a 16-bit register used to transfer data blocks between the ATA data buffer and the host. In addition, the Format Track command uses this register to transfer the sector-information. Setting this mode requires calling the Set Features command.

| bit-7 | bit-6 | bit-5 | bit-4 | bit-3 | bit-2 | bit-1 | bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| bit-15 | bit-14 | bit-13 | bit-12 | bit-11 | bit-10 | bit-9 | bit-8 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| D15    | D14    | D13    | D12    | D11    | D10    | D9    | D8    |

### 7.2.2 Error Register

The Error Register contains additional information about the source of an error. The information in the register is only valid when an error is indicated in ERR-bit (bit-0 = 1) of the Status Register. This register is valid when the BSY bit in Status register and Alternate

status register are set to "0"(Ready).

| bit-7 | bit-6 | bit-5                                                            | bit-4         | bit-3         | bit-2        | bit-1         | bit-0     |  |

|-------|-------|------------------------------------------------------------------|---------------|---------------|--------------|---------------|-----------|--|

| BBK   | UNC   | MC[0]                                                            | IDNF          | MCR[0]        | ABRT         | T0NF[0]       | AMNF      |  |

| DI    | BBK   |                                                                  | mark detec    | ted in the re | equested se  | ctor ID field | - Not     |  |

|       | DN .  | supported                                                        |               |               |              |               |           |  |

| U     | ١C    | Non-Correctable data error encountered                           |               |               |              |               |           |  |

| MC    | [0]   | Removable media access ability has changed - not supported (is   |               |               |              | orted (is 0)  |           |  |

| IDI   | NF    | F Requested sector ID-field Not Found                            |               |               |              |               |           |  |

|       |       | Media Change Request indicates that the removable-media drive's  |               |               |              |               |           |  |

| MC    | R[0]  | latch has changed, indicating that the user wishes to remove the |               |               |              |               |           |  |

|       |       | media - not supported (is 0)                                     |               |               |              |               |           |  |

| AB    | RT    | Drive statu                                                      | is error or A | borted inva   | id comman    | d             |           |  |

| TON   | F[0]  | Track 0 No                                                       | ot Found du   | ring a Reca   | librate comi | mand - Not    | supported |  |

| 0.N/  |       | Address Mark Not Found after finding the correct ID field - Not  |               |               |              |               |           |  |

| AM    |       | supported                                                        |               |               |              |               |           |  |

#### 7.2.3 Feature Register

This register enables drive-specific features. See the Set Features or Get/Set Features command descriptions.

|       | 1 A A A A A A A A A A A A A A A A A A A | 100 C |        |        |       |       |       |

|-------|-----------------------------------------|-------|--------|--------|-------|-------|-------|

| bit-7 | bit-6                                   | bit-5 | bit-4  | bit-3  | bit-2 | bit-1 | bit-0 |

|       | ~                                       | 4     | Featur | e byte |       |       |       |

#### 7.2.4 Sector Count Register

The Sector Count Register contains the number of data sectors requested to be transferred during a read or write operation between the host and the adapter. A zero register value specifies 256 sectors. The command was successful if this register is zero at command completion. If the request is not completed, the register contains the number of sectors left to be transferred.

This register's initial value is "01H"

Some commands (e.g. Initialize Drive Parameters or Format Track) may redefine the register's contents.)

| bit-7 | bit-6 | bit-5 | bit-4     | bit-3     | bit-2 | bit-1 | bit-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

|       |       |       | Sector co | ount byte |       |       |       |

©2009 PRETEC/C-One Technology Corp.

### 7.2.5 Sector Number Register

In the CHS (Cylinder, Head, Sector) mode, the Sector Number Register contains the subsequent command's starting sector number, which can be from 1 to the maximum number of sectors per track. In LBA (logical block address) mode, this register contains LBA bits 0-7, which are updated at command completion. See the command descriptions for register contents at command completion (whether successful or unsuccessful).

| bit-7  | bit-6 | bit-5      | bit-4       | bit-3   | bit-2 | bit-1 | bit-0 |

|--------|-------|------------|-------------|---------|-------|-------|-------|

| SN7    | SN6   | SN5        | SN4         | SN3     | SN2   | SN1   | SN0   |

| LBA7   | LBA6  | LBA5       | LBA4        | LBA3    | LBA2  | LBA1  | LBA0  |

| SN0 –  | SN7   | Sector nur | mber byte ( | 8-bits) |       |       |       |

| LBA0 – | LBA7  | LBA bits 0 | to 7        |         |       |       |       |

#### 7.2.6 Cylinder Low Register

In the CHS mode, the Cylinder Low Register contains the cylinder number low-8 bits and reflects their status at command completion. In LBA mode, this register contains LBA bits 8-15 and reflects their status at command completion.

| bit-7  | bit-6 | bit-5      | bit-4       | bit-3 | bit-2 | bit-1 | bit-0 |

|--------|-------|------------|-------------|-------|-------|-------|-------|

| CL7    | CL6   | CL5        | CL4         | CL3   | CL2   | CL1   | CL0   |

| LBA15  | LBA14 | LBA13      | LBA12       | LBA11 | LBA10 | LBA9  | LBA8  |

| CL0 -  | CL7   | Cylinder L | ow byte (8- | bits) |       |       |       |

| LBA8 – | LBA15 | LBA bits 8 | to 15       |       |       |       |       |

### 7.2.7 Cylinder High Register

In the CHS mode, the Cylinder High Register contains the cylinder numbers high-8 bits and reflects their status at command completion. In LBA mode, this register contains LBA bits 16-23 and reflects their status at command completion.

| bit-7   | bit-6   | bit-5      | bit-4         | bit-3  | bit-2 | bit-1 | bit-0 |

|---------|---------|------------|---------------|--------|-------|-------|-------|

| CH7     | CH6     | CH5        | CH4           | CH3    | CH2   | CH1   | CH0   |

| LBA23   | LBA22   | LBA21      | LBA20         | LBA19  | LBA18 | LBA17 | LBA16 |

| CH0 -   | - CH7   | Cylinder H | ligh byte (8- | -bits) |       |       |       |

| LBA16 - | - LBA23 | LBA bits 1 | 6 to 23       |        |       |       |       |

### 7.2.8 Drive Head Register

The Drive Head Register is used to select the drive and head (heads minus 1, when executing Initialize Drive Parameters command). It is also used to select the LBA addressing instead of the CHS addressing.

| bit-7   | bit-6 | bit-5                                         | bit-4                                     | bit-3        | bit-2       | bit-1         | bit-0     |  |  |  |

|---------|-------|-----------------------------------------------|-------------------------------------------|--------------|-------------|---------------|-----------|--|--|--|

| 1       | LBA   | 1                                             | DRV                                       | HS3          | HS2         | HS1           | HS0       |  |  |  |

| HS0-F   | 183/  | Head num                                      | ıber.                                     |              |             |               |           |  |  |  |

| DR      | V     | Drive sele                                    | ct number. '                              | When DRV:    | =0, the mas | ster drive is | selected. |  |  |  |

|         |       | When DR                                       | √=1, the Sla                              | ave drive is | selected.   |               |           |  |  |  |

| LBA24-l | BA27  | MSB of th                                     | e LBA addro                               | essing.      |             |               |           |  |  |  |

|         |       |                                               | Address mode select.                      |              |             |               |           |  |  |  |

|         |       | 0 = CHS (Cylinder, Head, Sector) mode.        |                                           |              |             |               |           |  |  |  |

|         |       | 1 = LBA (Logical Block Address) mode.         |                                           |              |             |               |           |  |  |  |

|         | ٨     | Logical Block address interrupted as follows: |                                           |              |             |               |           |  |  |  |

| LD      | LBA   |                                               | LBA07-LBA00 :Sector Number Register D7-D0 |              |             |               |           |  |  |  |

|         |       |                                               | LBA15-LBA08:Cylinder Low Register D7-D0   |              |             |               |           |  |  |  |

|         |       |                                               | LBA23-LBA16:Cylinder High Register D7-D0  |              |             |               |           |  |  |  |

|         |       | LBA27-LB                                      | A24:Drive/H                               | Head Regis   | ter HS3-HS  | 0             |           |  |  |  |

#### 7.2.9 Status Register

This register contains the adapter status. The contents of this register are updated to reflect the current state of the adapter and the progress of any command being executed by the adapter. When the BSY bit is equal to zero, the other bits in this register are valid. When the BSY bit is equal to one, the other bits in this register are not valid. When the register is read, the interrupt (#IREQ pin) is cleared.

| bit-7 | bit-6                                       | bit-5                                                              | bit-4                                                      | bit-3        | bit-2         | bit-1        | bit-0        |  |  |

|-------|---------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------|--------------|---------------|--------------|--------------|--|--|

| BSY   | DRDY                                        | DWF                                                                | DSC                                                        | DRQ          | CORR          | 0            | ERR          |  |  |

|       |                                             | When set, indicates that an error has occurred during the previous |                                                            |              |               |              |              |  |  |

| ER    | R                                           | command execution. The bits in the Error Register indicate the     |                                                            |              |               |              |              |  |  |

|       |                                             | cause.                                                             |                                                            |              |               |              |              |  |  |

| ID)   | IDX Index is not used – always set to Zero. |                                                                    |                                                            |              |               |              |              |  |  |

| COF   | סכ                                          | Indicates t                                                        | hat a data e                                               | error was co | orrected; tra | nsfer is not |              |  |  |

| COF   |                                             | terminated.                                                        |                                                            |              |               |              |              |  |  |

| DRQ   |                                             | Data Request. When set, indicates that the adapter is ready to     |                                                            |              |               |              |              |  |  |

| DR    | Q                                           | transfer a word or byte of data between the host and the adapter.  |                                                            |              |               |              |              |  |  |

| DS    | C                                           | Drive Seek Complete. When set, indicates that the requested        |                                                            |              |               |              |              |  |  |

| 50    | C                                           | sector was found.                                                  |                                                            |              |               |              |              |  |  |

| DW    | /=                                          | Drive Write Fault status. When set, indicates that an error has    |                                                            |              |               |              |              |  |  |

| DW    |                                             | occurred during write.                                             |                                                            |              |               |              |              |  |  |

|       |                                             | Indicates whether the adapter is capable of performing drive       |                                                            |              |               |              |              |  |  |

| וסח   | DRDY                                        |                                                                    | operations (commands). This bit is cleared at power up and |              |               |              |              |  |  |

|       |                                             | remains cleared until the drive is ready to accept a command. On   |                                                            |              |               |              |              |  |  |

|       |                                             | error, DRD                                                         | )Y changes                                                 | only after t | he host rea   | ds the Statu | us register. |  |  |

|     | This signal is set during the time the adapter accesses the   |

|-----|---------------------------------------------------------------|

| BSY | command buffer or the registers. During this time the host is |

| DOT | locked out from accessing the command register and buffer. As |

|     | long as this bit is set no bits in the register are valid.    |

#### 7.2.10 Alternate Status Register

The Alternate Status Register contains command block status information (see Status register). Unlike the Status register, reading this register does not acknowledge or clear an interrupt.

| bit-7 | bit-6 | bit-5 | bit-4 | bit-3 | bit-2 | bit-1 | bit-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BSY   | DRDY  | DWF   | DSC   | DRQ   | CORR  | 0     | ERR   |

#### 7.2.11 Device Control Register

The Device Control Register is used to control the drive interrupt request and issue an ATA soft reset to the drive.

| bit-7 | bit-6 | bit-5                                                               | bit-4    | bit-3 | bit-2 | bit-1 | bit-0 |  |

|-------|-------|---------------------------------------------------------------------|----------|-------|-------|-------|-------|--|

|       |       |                                                                     |          | 1     | SRST  | #IEN  | 0     |  |

| #IEN  |       | INTERRUPT ENABLE: When set (0), it enables interrupts to the        |          |       |       |       |       |  |

|       |       | host (using the #IREQ tri-state pin). When inactive (1) or drive is |          |       |       |       |       |  |

| #121  | - A.  | not selecte                                                         | high-Z). |       |       |       |       |  |

|       |       | This bit is ignored in Memory mode.                                 |          |       |       |       |       |  |

| SRST  |       | SOFT RESET: When set, forces the ATA to perform an AT disk          |          |       |       |       |       |  |

| 383   | I     | control soft reset operation.                                       |          |       |       |       |       |  |

### 7.2.12 Drive Address Register

This register reflects the drive and its heads. This register is provides for compatibility with the AT disk interface. It's recommended that this register is not mapped into this host's I/O space because of potential conflicts on bit7.

| bit-7       | bit-6 | bit-5                                                             | bit-4 | bit-3 | bit-2 | bit-1 | bit-0 |  |

|-------------|-------|-------------------------------------------------------------------|-------|-------|-------|-------|-------|--|

| High-Z      | #WTG  | #HS3                                                              | #HS2  | #HS1  | #HS0  | #DS1  | #DS0  |  |

| #DS0        |       | When set (0), it indicates that drive 0 is active and selected.   |       |       |       |       |       |  |

| #DS1        |       | When set (0), it indicates that drive 1 is active and selected.   |       |       |       |       |       |  |

| #HS0 - #HS3 |       | Negation of the head number in the Drive/Head Register.           |       |       |       |       |       |  |

| #WTG        |       | When set (0), it indicates that a write operation is in progress, |       |       |       |       |       |  |

|             |       | otherwise it is inactive (1) - not supported.                     |       |       |       |       |       |  |

Note:

Addressing Mode Descriptions - The adapter, on a command by command basis, can operate in either CHS or LBA addressing modes. Identify Drive Information tells the host

whether the drive supports LBA mode. The host selects LBA mode via the Drive/Head Register. Sector number, Cylinder Low, Cylinder High, and Drive/Head Register bits HS3=0 contain the zero-based LBA. The drive's sectors are linearly mapped with: LBA = 0 => Cylinder 0, head 0, sector 1. Regardless of the translation mode, a sector LBA address does not change. LBA = (Cylinder \* no of heads + heads) \* (sectors/track) + (Sector - 1).

This document provides information regarding to Pretec 2.5" Tiger IDE Solid State Drive product specification and is subject to change without any prior notice. No part in this report shall be distributed, reproduced, or disclosed in whole or in part without prior written permission of Pretec.